Integrierte Schaltkreise sind heute die EMV-Schwachstellen elektronischer Geräte

Die Integrationsdichte von Integrierten Schaltkreisen (IC) sowie deren interne Verarbeitungsgeschwindigkeit steigen immer weiter. Das bringt eine höhere Störempfindlichkeit hinsichtlich ihrer EMV mit sich. Schnelle Störimpulse, die in der Vergangenheit von den langsameren ICs noch nicht wahrgenommen wurden, können nun zu gravierenden Beeinträchtigungen führen, beispielsweise zu Signal- oder Funktionsfehlern. Pin-granulare Störfestigkeitsuntersuchungen an ICs zeigen Wege auf, wie zukünftig sogar robustere ICs hergestellt werden können.

Zur Sicherstellung einer hohen Robustheit von elektronischen Geräten gegenüber elektromagnetischen Störungen kann man die Eigenschaften von ICs nicht mehr außer Acht lassen. Burst- und ESD-Störungen dringen von außen in elektronische Geräte ein und gelangen über Leiterzüge bis an die Pins von ICs. Sowohl über die Pins als auch direkt über magnetische und elektrische Störfelder dringen die Störungen ins Innere der ICs vor. Die Auswirkungen auf die Funktion können unterschiedlich sein. Die Vielfalt reicht von flüchtigen tolerierbaren Fehlern, wie etwa kurzzeitiges Kippen eines Port-Ausgangs, bis zum Totalausfall, dauerhafter Funktionsverlust des ICs.

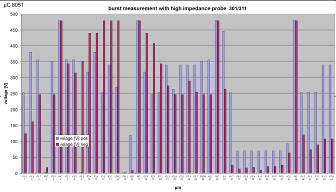

Unterschiedliche Störschwellen bei Mikrocontroller-Pins

In Bild 1 sind die Störschwellen dargestellt, die für die einzelnen Pins eines Mikrocontrollers – hier beispielhaft ein 8051 Derivat – ermittelt wurden. Die Messung erfolgte mit Störimpulsen von 1,5 ns (Anstieg) / 20 ns (Rückenzeit) der High-Impedanz-Probe P301 mit Amplituden zwischen +/- 5 V und 500 V. Diese Probe ist Bestandteil eines Testsystems, welches in [1] beschrieben ist. Die Störimpulse entsprechen den Störungen, die an den Pins eines ICs ankommen, wenn ein Gerät in Funktion einem Burst- oder ESD-Test unterzogen wird, bzw. in gestörter Industrieumgebung zum Einsatz kommt. Man erkennt, dass die Pins sehr unterschiedliche Störschwellen besitzen. An den Port-Pins ist zu erwarten, dass Eingänge immer bei der annähernd gleichen Störspannung schalten. Das ins Innere des ICs weitergeleitete Signal wird verfälscht. Entstehende Signalfehler haben bei diesem Beispiel in der Praxis keine Bedeutung, da Port-Signale vor der Weiterverarbeitung entsprechend gefiltert werden können. Eine Ausnahme bilden Pins, die den IC asynchron beeinflussen, beispielsweise das Reset-Pin 4 oder Pins, die sich direkt auf die gesamte Funktion des ICs auswirken, zum Beispiel der Quarzanschluss XTAL1-Pin 15. Oft, wie auch in diesem Beispiel, sind keine vorbeugenden Maßnahmen – Filter oder Ähnliches – im IC getroffen worden. Die Störschwelle liegt hier sehr niedrig bei < 5 Volt.

Wenn man die Fehlerbilder der Port-Pins auswertet, sind die Fehlerursachen nicht etwa weitergeleitete Signalfehler an den Core-Bereich. Diese sollten durch Softwaremaßnahmen beherrscht werden. Es handelt sich im Allgemeinen um schwerwiegende Fehler des gesamten ICs mit nachfolgendem erfolgreichem Wiederanlauf über Reset oder mit komplettem Absturz. Das bedeutet, dass über Einkopplung in Ports der Core-Bereich des ICs gestört wird.

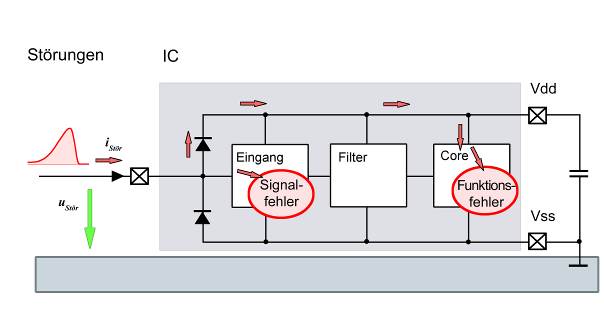

Signal- und Funktionsfehlern auf der Spur

Aus Bild 2 wird die Wirkungskette deutlich. Port-Störungen können zwei Wirkungslinien aufweisen.

Störspannung stört den Port und erzeugt Signalfehler.

Störstrom fließt über die Eingangsschutzdioden, das Vdd- und Vss- System bis in den Core-Bereich oder andere zentrale Funktionskomplexe wie PLL, Speicher und beeinflusst diese. Es entstehen schwere Funktionsfehler.

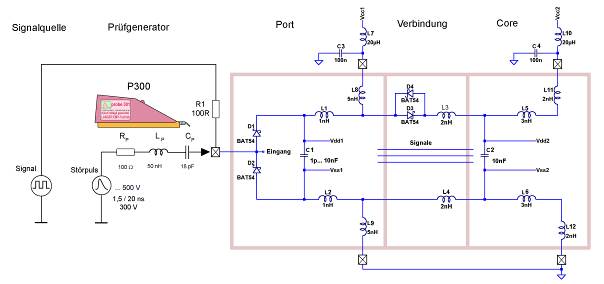

Zur weiteren Aufklärung muss der innere Aufbau des IC einbezogen werden. Ein auf diesen Zweck zugeschnittenes vereinfachtes Ersatzschaltbild ist in Bild 3 dargestellt.

Ein Störimpulsgenerator P300 und eine Signalquelle sind an den Port-Pin eines ICs angeschlossen. Der Prüfgenerator erzeugt Störimpulse mit 1,5 ns Anstieg und 20 ns Rückenzeit. Der Störimpuls wird über 18 pF in das Port-Pin eingekoppelt. Der IC besitzt einen Port- und Core-Bereich, die intern verbunden sind, im Beispiel durch zwei Dioden entkoppelt.

Schnelle transiente Vorgänge im IC-Inneren lassen sich nicht mit einem Oszilloskop messen. Deshalb werden die Wirkzusammenhänge im Weiteren simuliert.

Dabei sind die internen Induktivitäten (Bonddrähte und Metallebenen) von Bedeutung, externe Stützkondensatoren (C3, C4) und intern angeordnete Stützkondensatoren (C1, C2) an den Versorgungsleitungen.

Als erstes wird nur der Port-Bereich betrachtet, der Core-Bereich wird abgetrennt und C1 auf 1 pF eingestellt.

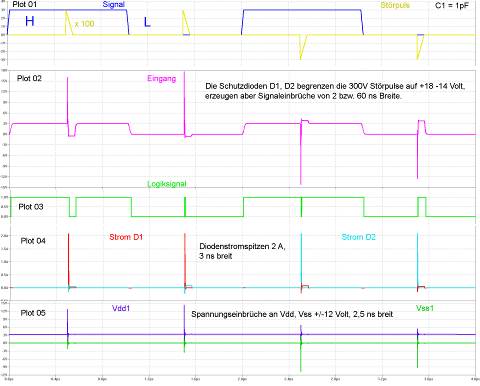

Bild 4 zeigt die Ergebnisse: Im Plot 01 sind das Signal der Signalquelle und der Störimpuls des Prüfgenerators um den Faktor 100 reduziert dargestellt. Plot 02 zeigt die Wirkung beider Ereignisse am Port-Pin. Der Störimpuls wird durch die Koppelkapazität CP des Prüfgenerators differenziert und durch die Schutzdioden des Ports begrenzt. Die Begrenzung des Nadelimpulses (Störimpulsvorderflanke) wird durch die im Vdd- und Vss-Zweig liegenden Induktivitäten (L1, L2, L8 und L9) gehemmt. Es entstehen Spannungsspitzen bis zu 18 V am Eingang. Die Port-Schaltung, nicht dargestellt, wandelt die Spannung am Eingang (Plot 02) in ein Logiksignal (Plot 03).

Moderne ICs leiden unter schnellen Störimpulsen

Durch die Eingangsschutzdioden fließen Strompulse der Breite von 3 ns mit einem Spitzenwert von 2 A in das Vdd- und Vss-Netz (Plot 04). Sie erzeugen an den Leitungsinduktivitäten des Vdd- und Vss-Netzes Spannungen bis 12 V (Plot 05). Das bedeutet, dass alle an das Versorgungssystem angeschlossenen CMOS-Zellen ihre logischen Zustände verändern können. Ein Einbruch am Vdd-Zweig um 3 V ist gleichzusetzen mit dem Abschalten der Versorgungsspannung, in diesem Fall für 3 ns. Speicherzellen / Register werden ihren logischen Inhalt verlieren. Die Wirkung hängt natürlich von der Trägheit (Eigenkapazität) der Zellen ab. Nur wenn die Zellen schnell genug sind, kann eine Umladung und damit Beeinflussung erfolgen. Aus diesem Grund führten vor Jahren, als die ICs noch langsamer waren, schnelle Störimpulse nicht zur Beeinflussung. Moderne ICs leiden unter schnellen Störimpulsen und werden gestört.

Um hochfrequente Spannungsdifferenzen zwischen Vdd- und Vss-Zweig kurzzuschließen, sind Stützkondensatoren vorgesehen. Wegen der im Vdd- / Vss-Zweig vorhandenen Längsinduktivitäten müssen diese jedoch im IC angeordnet werden. Externe Abblockungen wirken bei schnellen Störflanken nicht. Die interne Stützkapazität kann aus speziellen CMOS-Zellen gebildet werden.

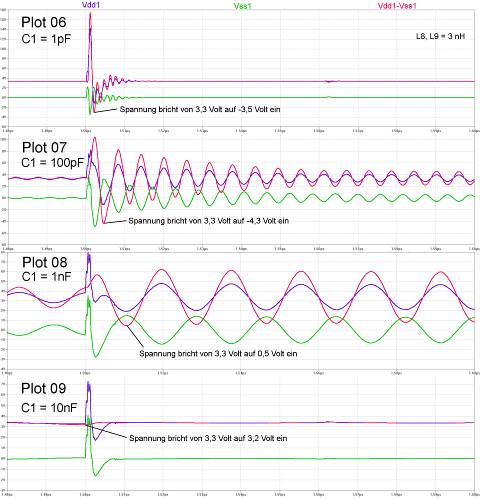

In Bild 5 ist die Wirkung der internen Abblockung des Vdd- / Vss-Systems mit unterschiedlichen Kapazitätswerten dargestellt. Die Wirkungen des Störimpulses wurden gedehnt abgebildet.

| C1 = 1pF: | Der Störimpuls setzt sich dominant durch und erzeugt pulsförmige Spannungsdifferenzen zwischen Vdd und Vss (Plot 06). |

| C1 = 100pF | Der Störimpuls wird fast gleich auf Vdd und Vss verteilt (bei 1,5 µs), so dass durch ihn kaum Differenzspannungen entstehen. Allerdings ist der angestoßene Einschwingvorgang auf Vdd und Vss gegenphasig und erzeugt nachfolgend hohe Differenzspannungen im internen Versorgungssystem (Plot 07) |

| C1 = 1nF | Durch den Kondensator C1 wird der Störimpuls vollständig gleichmäßig auf Vdd und Vss verteilt, so dass durch ihn keine Differenzspannung entsteht. Jedoch entsteht ebenfalls ein gegenphasiger Einschwingvorgang, der noch höhere Differenzspannungen erzeugt (Plot 08). |

| C1 = 10nF | Durch den relativ großen Kondensator C1 wird der Störimpuls vollständig gleichmäßig auf Vdd und Vss verteilt, so dass durch ihn keine Differenzspannung erzeugt wird. Das System schwingt nicht mehr an, so das keine Differenzspannung Vdd1 / Vss1 entsteht (Plot 09). |

Sinnvolle Entstörmaßnahmen

Eine wichtige Erkenntnis ist, dass neben den direkten Spannungseinbrüchen durch den Störimpuls Einschwingvorgänge angestoßen werden, die zwischen Vdd und Vss Differenzspannung erzeugen und den IC regelrecht abschalten. Der notwendige Wert des Stützkondensators liegt zwischen 1 und 10 nF. Da zusätzliche Kondensatoren im IC Kosten verursachen, sollte der minimal erforderliche Wert durch Simulation ermittelt werden. Seit etwa 2005 wurde begonnen, Stützkondensatoren mit einigen nF in ICs zu integrieren.

Damit ist das Beeinflussungsproblem des ICs noch nicht vollständig gelöst. In Bild 5, Plot 09 wird die Spannung Vdd und Vss im Gleichtakt um 3,1 Volt angehoben. Wenn der Port-Bereich, Bild 2, mit dem Core-Bereich verbunden wird, werden diese Gleichtaktimpulse als Differenz zwischen den beiden Bereichen stehen. Das kann Signalverbindungen stören. Dieses Fehlerprinzip kann auch zwischen anderen, getrennt versorgten Bereichen wirken, wie etwa bei PLLs, Quarzoszillatoren oder Speichern.

Für Plot 10, Bild 6, wurde die gesamte Schaltung, Bild 2, aktiviert. Dabei war der Port-Bereich mit C1 = 1pF nicht und der Core-Bereich mit C2 = 10 nF gut abgeblockt. Das entspricht praktischen Anordnungen. Es entstehen Differenzspannungen von reichlich 3 Volt zwischen den Versorgungen beider Bereiche. Diese Differenzspannungen können die zwischen den Bereichen liegenden Signalverbindungen stören. Wenn man den Port-Bereich ebenfalls mit 10 nF abgeblockt, wird die Differenzspannung gemindert. Das erfordert zusätzliche Kapazität, die in einem IC wirtschaftlich nicht realisierbar ist. Eine bessere Lösung erzielt man mit der Verminderung der Längsinduktivitäten L1 bis L4 des internen Vdd- / Vss-Systems und erreicht damit, dass die externen Stützkondensatoren wirken können. Niederimpedante und flächige Versorgungssysteme sind Bestandteil einer Entstörstrategie, die auf Board-Ebene um 1995 mit großem Erfolg eingeführt wurde. Auf ICs angewendet, ist das Ergebnis in Bild 7 dargestellt. Die Wirkung ist deutlich: Zwischen Vss1 und Vss2 gibt es keinen Spannungseinbruch mehr. Nur der Bahnwiderstand, der in der Simulation verwendeten Dioden, erzeugt noch einen Einbruch zwischen Vdd1 und Vdd2 von rund 1 Volt. Praktisch bedeutet das eine Vermaschung des Vdd- / Vss-Systems. Vdd und Vss müssten je eine separate Metalllage im Die des IC erhalten.

Umstellen von Stern- auf vermaschte Massesysteme

Die Metalllagen müssten, um entsprechend niedrige Induktivitätswerte zu erhalten, aus eng vermaschten Leitungsnetzen oder aus einer geschlossenen Metallfläche bestehen. Das widerspricht jedoch der Tradition des IC- Designs. Nach dieser Tradition wurden bisher intern sternförmige Versorgungsnetze verwendet, die eine hohe Längsinduktivität besitzen. Die Verbindung der Versorgungsinseln erfolgte erst auf dem Board. Aufgrund dieser Tatsache waren die ICs unzureichend störfest. Für den Anwender entstanden zusätzlicher Entwicklungsaufwand und zusätzliche Kosten zur Entstörung der Elektronikbaugruppen. Aus Tradition hat man den Weg der inneren sternförmigen Leitungsführung nicht verlassen.

Als auf Board-Ebene Mitte der neunziger Jahre die Umstellung von der Sternlösung auf vermaschte Massesysteme oder Flächenmassesysteme begann, stieß dieses Vorhaben auf erhebliche Widerstände unter den Fachleuten, denn man glaubte aus der Tradition heraus, an die sternförmigen Massesysteme. Der Erfolg nach der Umstellung überzeugte schließlich. Dennoch dauerte die Umstellung in den Firmen meist mehrere Jahre und ist noch nicht komplett abgeschlossen.

Bei den ICs ist erst jetzt die Zeit reif, mit einer derartigen Umstellung zu beginnen.

Wichtige Erkenntnisse führen zukünftig zu robusteren ICs

Aus der Methode der pin-granularen Störfestigkeitsuntersuchungen an ICs lassen sich eine Reihe von Erkenntnissen gewinnen, die in der Zukunft zu robusteren ICs führen wird, trotz der fortschreitenden Erhöhung der Integrationsdichte und der damit verbundenen höheren Störempfindlichkeit:

- Steilflankige Störströme fließen über Schutzdioden in das Vdd- / Vss- Netz

- Es kommt zu Spannungseinbrüchen im Vdd- / Vss-System

- In Abhängigkeit von internen Induktivitäten und realisierbaren Kapazitäten kann es zu Einschwingvorgängen im Vdd- / Vss-System kommen

- Es kommt zu induktivitätsbedingten Längsspannungsabfällen im Vdd- / Vss-System, zu Spannungsdifferenzen zwischen entkoppelten Bereichen

- Interne Kapazitäten geeigneter Größe helfen, diese Vorgänge zu minimieren

- Zielführend ist eine Vermaschung der Versorgungssysteme auf IC-Ebene