Probleme auf IC-Ebene finden und beheben

Moderne elektronische Geräte werden kleiner, komplexer und erfordern immer leistungsstärkere integrierte Schaltkreise (ICs). Wenn die ESD-Immunität eines Geräts erst in der letzten Entwicklungsphase getestet wird, sind erkannte Probleme nur schwierig, zeitaufwändig und teuer zu lösen. Das Testen eines Geräts oder seiner einzelnen Komponenten während des anfänglichen Entwurfszyklus ist daher effizienter und kann unter Verwendung eines speziellen Testaufbaus durchgeführt werden.

Dieser Artikel konzentriert sich auf die Auswirkungen des IC-Verhaltens auf das elektronische Design, insbesondere auf die Eigenschaften der elektrostatischen Entladung und beschreibt die Beeinflussung des IC auf das Gerät.

I. Einflüsse auf den IC in der Elektronik

Die Anfälligkeit eines IC für schnelle Impulsstörungen wie ESD steigt signifikant an, wenn seine baulichen Abmessungen, Betriebsspannungen und Betriebsschwellen verringert werden. Entwicklungen im ASIC- und Mikrocontroller-Design tendieren zu Strukturen kleiner als 100 nm. In Verbindung mit höheren Schaltraten führt dies zu einer Abnahme der Störfestigkeit um etwa 90 Prozent - ein Rückgang, der sich auch im EMV-Verhalten des Geräts widerspiegelt.

Bei identischer Funktionalität geben die guten EMV-Eigenschaften eines IC Herstellern einen Vorteil gegenüber Wettbewerbern. Daher ist es das Ziel des Ingenieurs, die für die Störfestigkeit entscheidenden Parameter zu bestimmen und das Ziel des Elektronikentwicklers, einen möglichst robusten IC zu verwenden.

Während ESD-Teststandards auf Geräteebene seit Jahren verfügbar sind, gibt es keine derartigen Bestimmungen für die einzelnen Teile eines Geräts (wie Baugruppen und Komponenten). Die zunehmende Komplexität und insbesondere die zunehmende Dichte der Komponentenintegration erschweren die Einhaltung der Vorrichtungsstandards, ohne dass auf IC-Ebene definierte Bedingungen vorliegen.

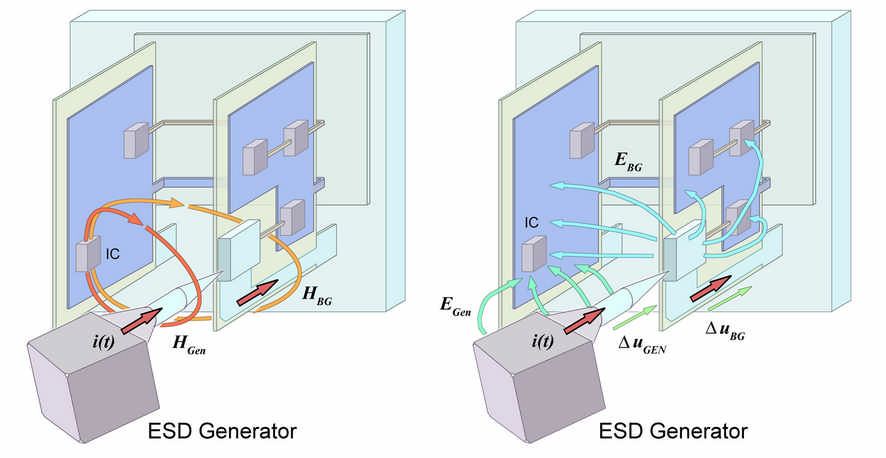

IC-Testimpulse werden auf Basis von Gerätetestverfahren definiert. Die jeweiligen Testaufbauten erzeugen elektrische und magnetische Felder im Gerät. Diese Felder wirken sich lokal auf die Schnittstelle des IC-Pakets aus. IC-Testgeneratoren müssen die durch diese elektrischen und magnetischen Felder verursachten Störungen universell simulieren können. Eine existierende Methode zum individuellen Testen eines IC ist das Human Body Model (HBM), obwohl seine Ergebnisse der ESD-Immunität keinen Einfluss auf das ESD-Verhalten des Geräts während des Betriebs haben. Daher sind Schutzmechanismen, die diese Tests bestehen, keine praktikablen Lösungen und können die Immunität des Geräts negativ beeinflussen - sogar zum Ausfall des Geräts führen.

II. ESD-Charakteristik

Um im Test vorhandene ESD-Interferenzen zu verstehen, muss man in der Lage sein, die von der verwendeten ESD-Pistole erzeugten Interferenzen zu identifizieren und deren Unbekannte (wie Interferenzform usw.) zu analysieren. Während der Strom, den die Spitze des ESD-Generators emittiert, in der Norm beschrieben wird, unterscheidet er sich von den elektrischen und magnetischen Feldern, die sowohl vom Körper als auch von der Spitze des Objekts ausgehen.

Die Pulsformen dieser Felder unterscheiden sich vom Störstrom und stören das elektronische Gerät zusätzlich, wobei die gewünschte Wirkung möglicherweise überschritten wird. Inwieweit diese Felder das elektronische Gerät stören, hängt von der Positionierung des ESD-Generators in Bezug auf die Gerätemodule ab. Wenn der ESD-Generator gedreht oder gekippt wird, können Schwachstellen im Gerät rein zufällig reagieren, wodurch die Erkennung und Analyse von Funktionsfehlern eines Geräts und deren Ursache-Wirkungs-Beziehung unmöglich wird.

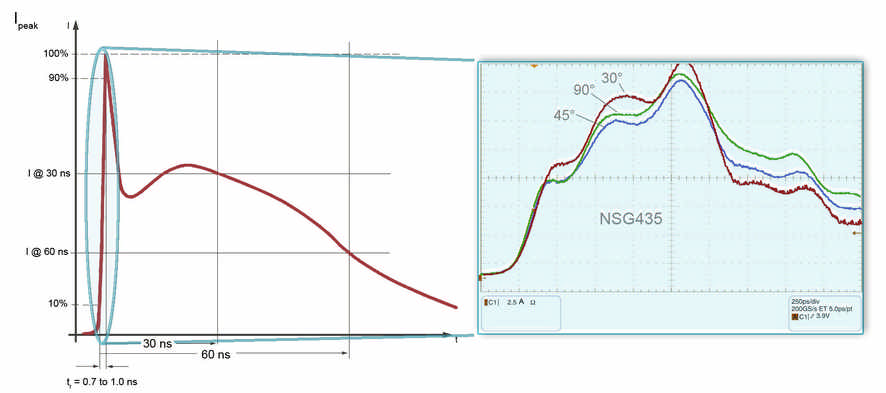

Die typische ESD-Impulsform, wie in der Norm 61000-4-2 (Abbildung 2) beschrieben, wurde unter Verwendung eines Testaufbaus und eines bis zu 4 GHz kalibrierten Oszilloskops gemessen. Im ersten Peak sind verschiedene, nicht identifizierbare Abweichungen vom Standard erkennbar. Die ansteigende Flanke des ESD-Impulses ist das bedeutendste Ereignis, da sich die Strom- und Spannungsänderung am schnellsten ändern und eine sehr starke elektrische und magnetische Kopplung verursachen. In der Impulsform sind auch hochfrequente Transienten mit Anstiegszeiten von bis zu 100 ps zu erkennen, die ein leichteres Eindringen in die Elektronik ermöglichen.

Jede der drei Farben, welche in Abbildung 2 dargestellt sind, repräsentiert eine Impulsform, die auf einem unterschiedlichen Winkel und einer anderen Handhabung des ESD-Generators während des Tests basiert. Obwohl alle in den Anwendungsbereich der Norm fallen, bezeugen diese Abweichungen die Ungenauigkeit der Testergebnisse.

Der Effekt ist noch deutlicher, wenn die tatsächliche Interferenz an einer IC-Kurve oszilliert wird. Wird der ESD-Generator an einem der abgeschirmten Steckverbinder des Schnittstellenmoduls kontaktiert und der Störstrom eingekoppelt, dann wird der Störstrom umgeleitet und fließt durch das GND-System zur Elektronikplatine, auf der sich der IC befindet, und wo Messungen an den Leiterbahnen durchgeführt werden.

Obwohl die IC-Leiterbahnen nicht an den abgeschirmten Stecker angeschlossen sind, werden am IC-Eingang erhebliche Störungen bis zu 70 V gemessen. Diese Störungen können sich zum Beispiel über die magnetische Kopplung im Steckverbinder zwischen dem Schnittstellenmodul und der Elektronikplatine in die Leiterbahnen einkoppeln. Die ESD-Störung kann in andere Spuren eingekoppelt werden, da ihr Strom nur in die Abschirm- und GND-Systeme fließt. Der Board-to-Board-Anschluss im Entladungspfad der ESD-Störung hat auch eine Impedanz, die zu einem Spannungsabfall zwischen den beiden Leiterplatten führt. Das resultierende elektrische Feld kann auch in die Signalspuren oder in ähnliche Teile auf der Leiterplatte einkoppeln. In Abbildung 2 wird deutlich, dass keine Korrelation zwischen der resultierenden Störung am IC-Eingang und der tatsächlichen ESD-Impulsform besteht. Teile der gemessenen Impulse sind kürzer als 200 ps.

III. Feldeinflüsse am IC

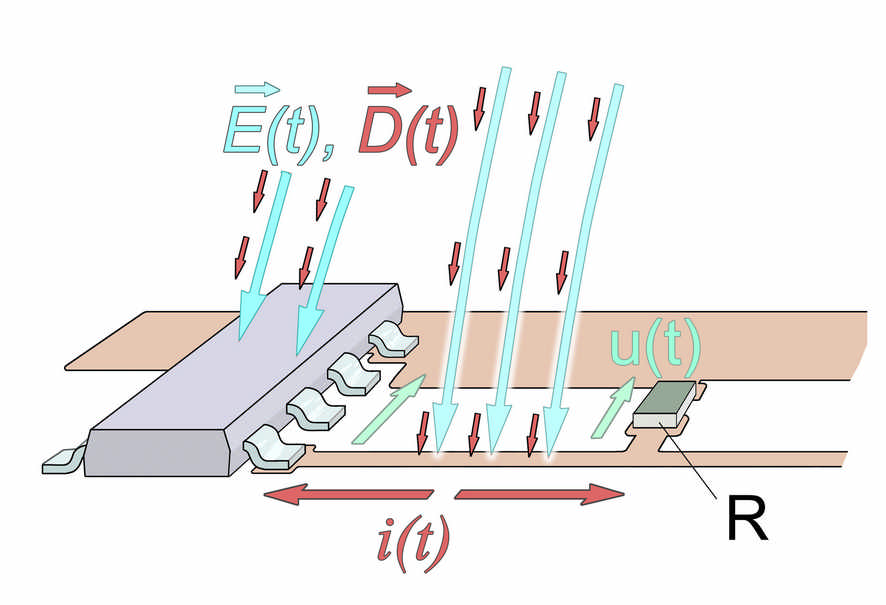

Leitungen mit hoher Impedanz sind hauptsächlich empfindlich gegen elektrische Störungen. Die Spannungsdifferenz zwischen der Schaltung und ihrer Umgebung (z. B. Metallteile, ESD-Generator usw.) erzeugt ein elektrisches Feld, das die Signale oder die Schaltung beeinflussen kann. Ein solcher Spannungsunterschied kann auftreten, wenn beispielsweise eine ESD-Kontaktentladung an einem nahegelegenen Metallteil vorgenommen wird. Der Entladungspfad des Störstroms hat eine Impedanz. Zusätzlich besteht zwischen dem Metallteil und der Elektronik ein Spannungsabfall, der die Elektronik über das elektrische Feld beeinflusst. Der resultierende Spannungsimpuls kann die Leiterbahnen oder, abhängig von seiner Empfindlichkeit, den IC direkt stören. Daraufhin kann eine Signalverfälschung oder die Störung, die andere Bereiche des IC erreicht, beispielsweise durch Schutzdioden, folgen, was weitere Probleme verursacht.

Kritische Pins oder Leitungen umfassen Reset-, Takt-, Quarz-, Test-Pins oder hochohmige Messeingänge von A/D-Wandlern.

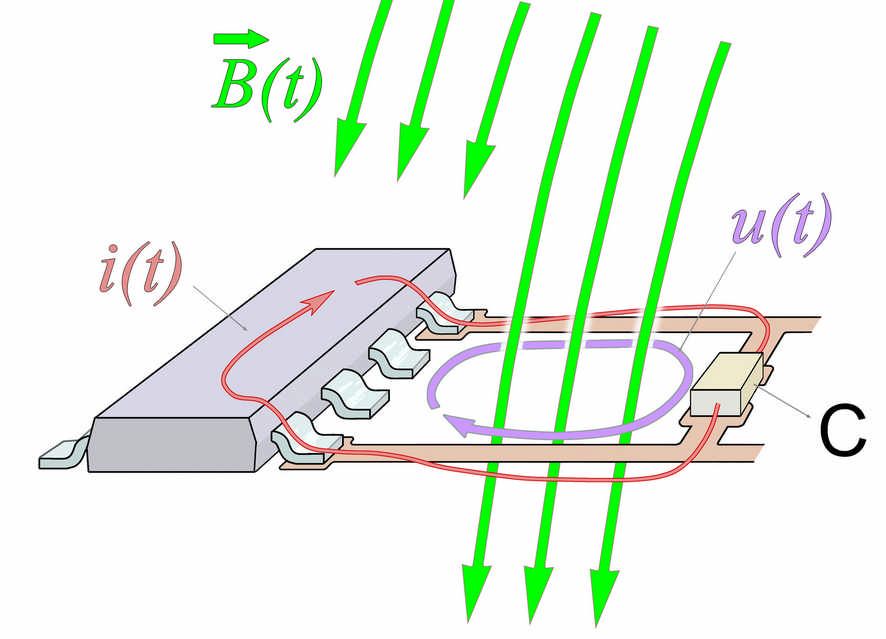

Im Falle einer magnetischen Interferenz erzeugt der Störstrom ein entsprechendes Magnetfeld im Gerät. Dieser Störstrom kann auch als Folge einer Kontaktentladung bei niederohmig verbundenen Metallteilen auftreten. Der abgeleitete Strom ist immer mit dem Magnetfeld verbunden und abhängig vom Prüfaufbau. Dieses resultierende Magnetfeld kann eine Störspannung in vorhandenen Schleifen wie Leitungsnetzen auf der Leiterplatte induzieren. Dieser Störimpuls fällt bei hochohmigen IC-Eingängen ab und stört diese daher. Darüber hinaus kann die Störung auch andere Bereiche innerhalb des IC betreffen, wie z. B. die PLL, den Core usw. In Bezug auf Magnetfeldstörungen umfassen kritische Leitungen das Stromversorgungssystem, niederohmige Signale und Leitungen, die über einen Kondensator mit GND oder der Stromversorgung verbunden sind.

Die Kopplungsmechanismen des elektrischen Feldes werden durch die Kapazität zwischen den Leitungsnetzen des IC und seiner Umgebung bestimmt. Die Störung wird abgeleitet, wenn ein mit niedriger Impedanz abgeschlossener IC-Eingang kapazitiven Störungen ausgesetzt wird. Wenn die Leitungen hochohmig verbunden sind, wird der Störimpuls direkt über den kapazitiven Spannungsteiler übertragen. Letztendlich sind die Auswirkungen auf den IC ähnlich wie bei der magnetischen Kopplung.

Der Koppeleffekt des Magnetfelds kann mit einem Transformator verglichen werden. Die Interferenz mit den niederohmigen Schleifen des IC führt zu einem induktiven Stromteiler. Der vom Störgenerator erzeugte Störstrom wird an die Leitungsnetze des IC übertragen. IC-Eingänge mit niedriger Impedanz führen zur Differenzierung des Störimpulses durch das Magnetfeld. Die induzierten Impulse haben viel schnellere Anstiegszeiten und sind kürzer als die tatsächliche Störung, die vom ESD-Generator erzeugt wird. Heutige Schaltungen sind schnell genug, um diese abgeleiteten Störungen auszuwerten und zu beeinflussen, die viel kürzer als 1 ns sein können.Um nützlich zu sein, müssen Testverfahren die Feldstörungen im Gerät simulieren. Eine sehr niederohmige Quelle von viel weniger als 50 Ohm ist erforderlich, um die Störungskopplung über das Magnetfeld in den IC-Pin zu simulieren. Dadurch kann eine Störung durch Spannungsinduktion im IC oder in den Leitungsnetzen erzeugt werden. Ein Störungsgenerator mit einer sehr hohen Impedanz, viel höher als 50 Ohm, ist erforderlich, um die elektrische Kopplung zu simulieren. Dies ermöglicht in Verbindung mit einer sehr geringen Koppelkapazität die Simulation elektrischer Interferenzen.

IV. IC-Testsystem

Ein von Langer EMV-Technik entwickeltes Testsystem umfasst Generatoren der Serien 200 und 300, die entsprechend den Mechanismen konstruiert wurden, mit denen Impulse in elektronische Baugruppen eingekoppelt werden und diese physikalischen Interferenzen exakt simulieren.

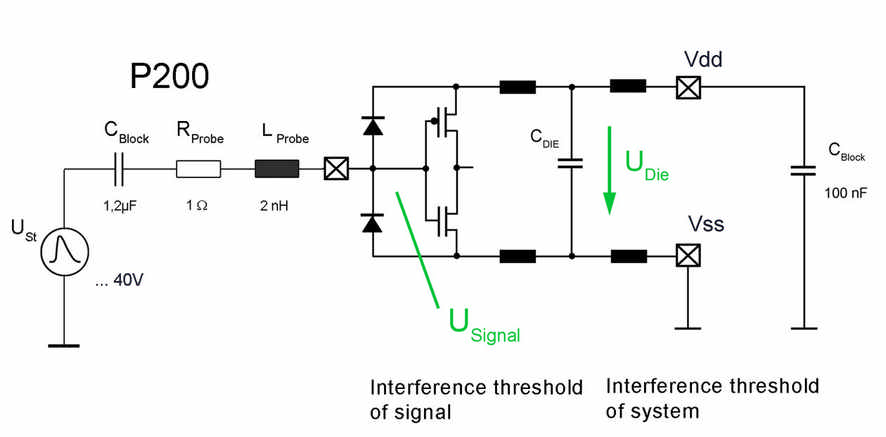

Der Effektmechanismus des Magnetfelds wird durch den Parameter einer externen IC-Schleife und das entsprechende Impulsmagnetfeld charakterisiert. In der praktischen Anwendung können diese Induktivitätsschleifen durch kapazitiv gegen GND kurzgeschlossene Leiterbahnen erzeugt werden (zum Beispiel Vdd mit Überbrückungskondensator). In diesen Schleifen wird die Spannung mit einem Spitzenwert von etwa 40 Volt induziert. Die Generatoren der 200-Serie wurden entwickelt um diese Eigenschaften nachzubilden. Sie bestehen aus einer Impulsspannungsquelle und einem Koppelnetz. Der Spitzenwert der Impulsspannungsquelle ist einstellbar und wird als Generatorspannung bezeichnet. Dies ist die vom Generator erzeugte Störgröße. Die Reihenschaltung von Widerstand und Induktivität bestimmt die Stromwerte. Der Generator ist daher so aufgebaut, dass er einen niedrigen Widerstand von etwa 1 Ω und eine geringe Induktivität von etwa 2 nH aufweist. Die interne Kapazität sorgt für die galvanische Trennung von GND. Dadurch können die Versorgungspins getestet werden und der Kondensator des Generators kann als Sperrkondensator wirken.

Die Generatoren der 300-Serie, mit denen Störungen durch elektrische Feldimpulse simuliert werden, koppeln eine Störung mit einer Anstiegszeit um eine Nanosekunde über einen 18 pF-Koppelkondensator in den IC-Pin. Der interne Widerstand der Quelle beträgt 150 Ohm und hat eine Induktivität von 50 nH - eine relativ hohe Impedanz. Die Störung wird über die Schutzdioden mit Vdd/Vss im IC kurzgeschlossen. Der Generator dient als Impulsstromquelle. Der Stromimpuls wird hauptsächlich durch die internen Parameter des Generators bestimmt. Die resultierende maximale Leerlaufspannung beträgt 500 V und entspricht den realen Bedingungen.

Mit den IC-Testsystemen von Langer EMV-Technik kann das Verhalten von ICs durch gezielte Störungen untersucht werden, unabhängig davon, ob sie vom Feld oder über die Leitung geleitet werden oder ob Emission oder Immunität getestet werden.

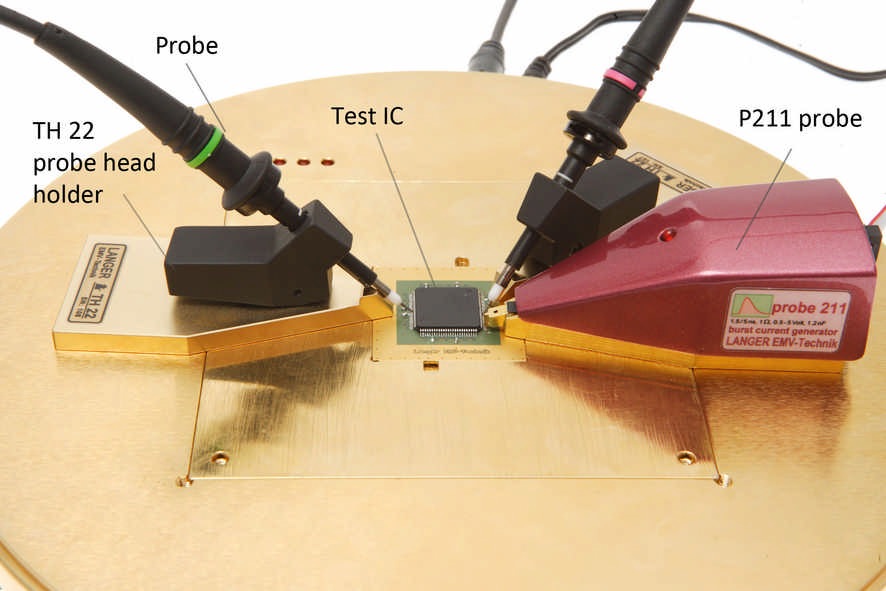

Der IC wird im Normalbetrieb getestet. Dazu wird der IC aus seiner Anwendung genommen und auf eine spezielle Testleiterplatte platziert. Die Testleiterplatte ist mit der erforderlichen Schaltung des DUT sowie mit Filtern für alle erforderlichen Versorgungsspannungen und -signale ausgestattet, um die Funktionalität sicherzustellen. Der hochfrequenzkompatible Aufbau des DUT wird durch die massive Metallplatte, die als Referenz-GND dient, und die Messungen auf engem Raum gewährleistet, sichergestellt. Die Anwendung ist über einen nach unten gerichteten Stecker verbunden. Somit wird nur der Prüfling oben auf dem System platziert und alle anderen Komponenten werden unterhalb der GND-Einheit entkoppelt. Diese Anforderungen sind entscheidend, damit Messungen reproduzierbar sind. Das Messsystem muss nicht in die Testleiterkarte integriert sein, sondern befindet sich in den entsprechenden Generatoren. Das System wurde für alle IC-Messungen erstellt.

Einige Arten von Fehlern, die dazu führen können, dass der Controller nicht mehr funktioniert, sind einfache Datenfehler, Reset-Auslösung oder Hardwarefehler. Nicht reversible Fehler wie ein Latch-up oder Fehler in der internen Oszillatorschaltung treten manchmal bei hohen Störungspegeln auf. Bestimmte Bereiche des Controllers reagieren empfindlicher auf Störungen. Eine Fehlerursache kann der Controller-Kern sein, der sich in dieser Region befindet. Maßnahmen, die der Benutzer ergreifen muss, um Geräte gegen Störungen immun zu machen, hängen von der Konstruktion und Funktion des einzelnen Geräts ab. Anfällige Leitungen müssen zwischen GND-Schichten eingeschlossen werden, um beispielsweise elektrische oder magnetische Felder zu blockieren. Diese Leitungen können auch durch Filterelemente geschützt werden. Die Sperrkondensatoren in der Nähe des Versorgungspins reduzieren die Größe der Schleife, wo möglicherweise Störspannungen induziert werden können.

Die Implementierung der Testsysteme ermöglicht ein besseres und umfassenderes Verständnis des EMV-Verhaltens von ICs. Durch dieses Wissen kann der elektronische Entwickler das EMV-Verhalten des gesamten Geräts verbessern.