使用朗格尔(Langer EMV-Technik GmbH)近场探头实现至6 GHz的测量

使用朗格尔技术有限公司(Langer EMV-Technik GmbH)的多种近场探头、PA 306前置放大器(100 kHz - 6 GHz, 30分贝, 噪声系数3dB)和ChipScan-ESA芯片扫描软件,可实现频率至6 GHz的测量。

ChipScan-ESA 芯片扫描软件不仅可以远程控制频谱分析仪,还能够为开发工程师提供以下功能:

- 分析比较测量曲线

- 校正函数和校正系数的换算

对LVDS系统进行至6 GHz的测量

在实际应用中,LVDS传输系统往往是干扰发射问题的原因。这些问题经常会与连接器和电缆有关。实践中普遍认为,对称的LVDS信号(差模信号)不会引起干扰,而其含有的共模信号却很容易产生输出耦合。下面的例子通过测量LVDS100驱动器(2Gbps)与接插连接器来详细阐明这些关系。

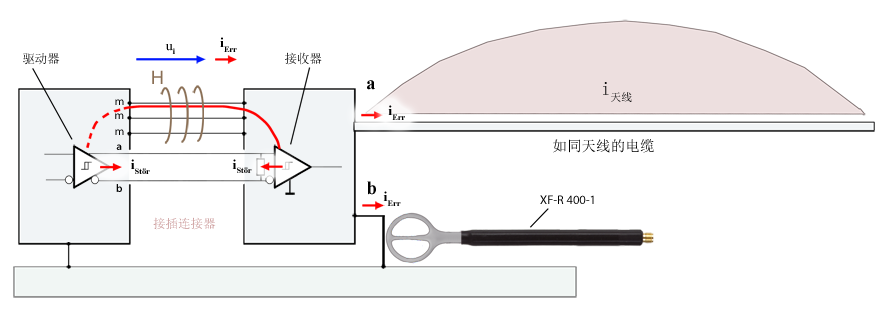

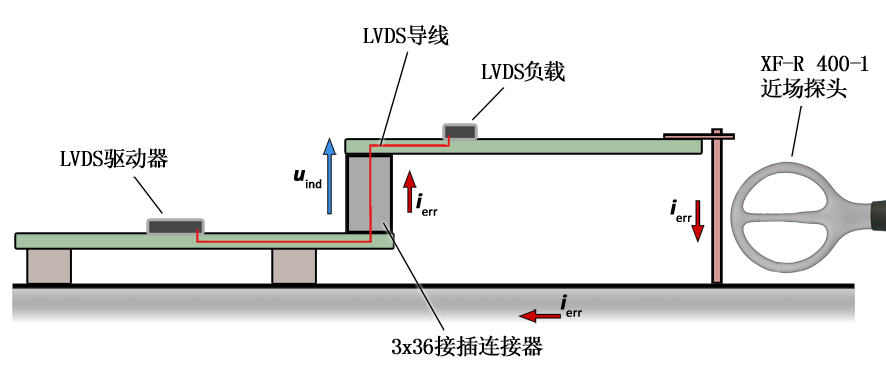

图1所示为干扰产生过程的原理图。LVDS驱动器的差模电流和共模电流iStör流经LVDS的a、b线及接插连接器流入接收器,然后通过连接器的接地引脚m返回到驱动器,从而引发干扰发射(图1)。他们在接插连接器的接地引线m中产生自感电压ui,而这个电压引发接插连接器接地引脚m的干扰电流iErr。此干扰电流被驱动流入连接的电缆上(图1,a端口),此时的电缆效果如同发射天线。测量时应该使用端口b,而不用端口a。使用磁场探头XF-R 400-1能够测量出该端口的激励电流iErr(使用ChipScan-ESA 芯片扫描软件的电流校正因数)。导致激励电流iErr并由此而产生干扰发射的原因是驱动器的共模和差模电流。这些电流在接插连接器的接地引脚m产生激励电流iErr,从而引发干扰发射。

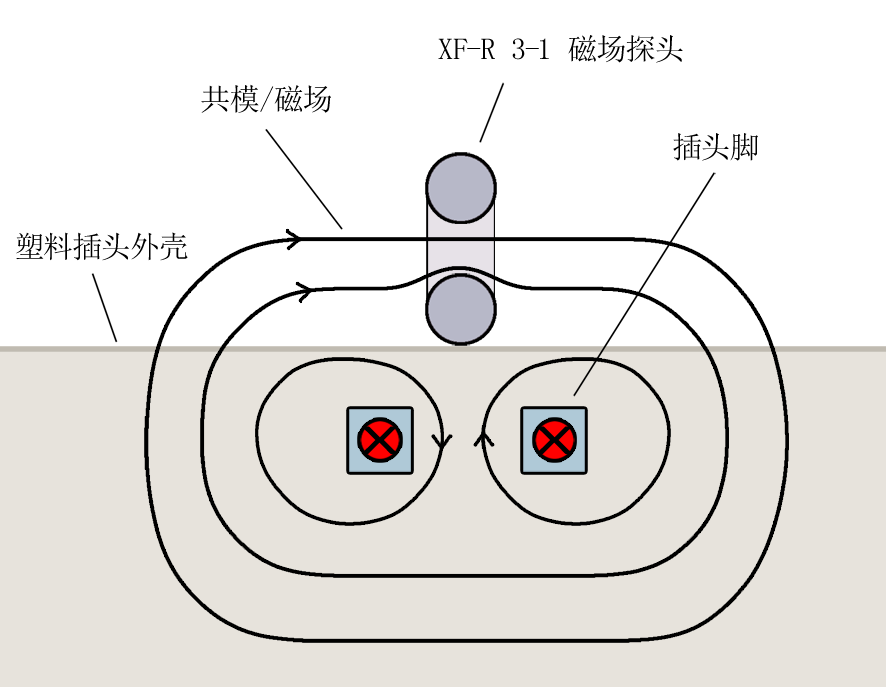

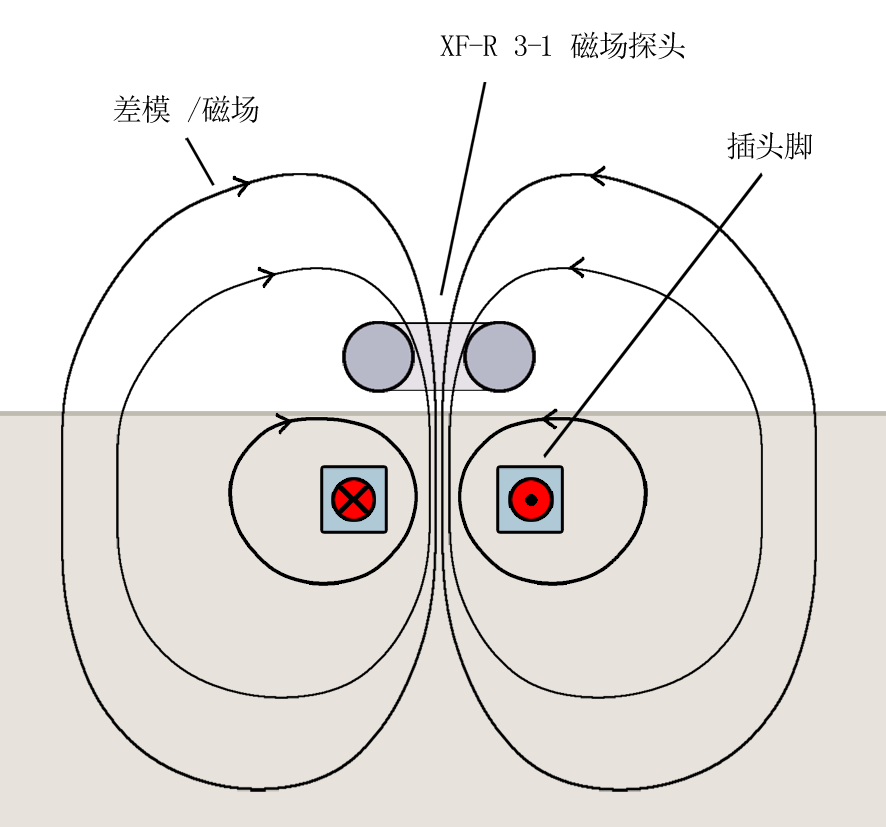

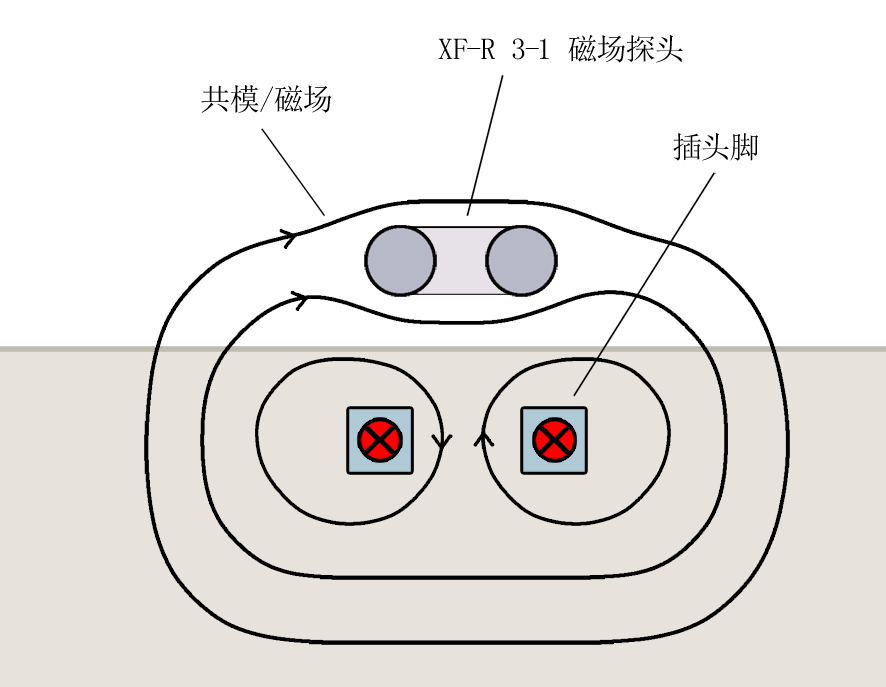

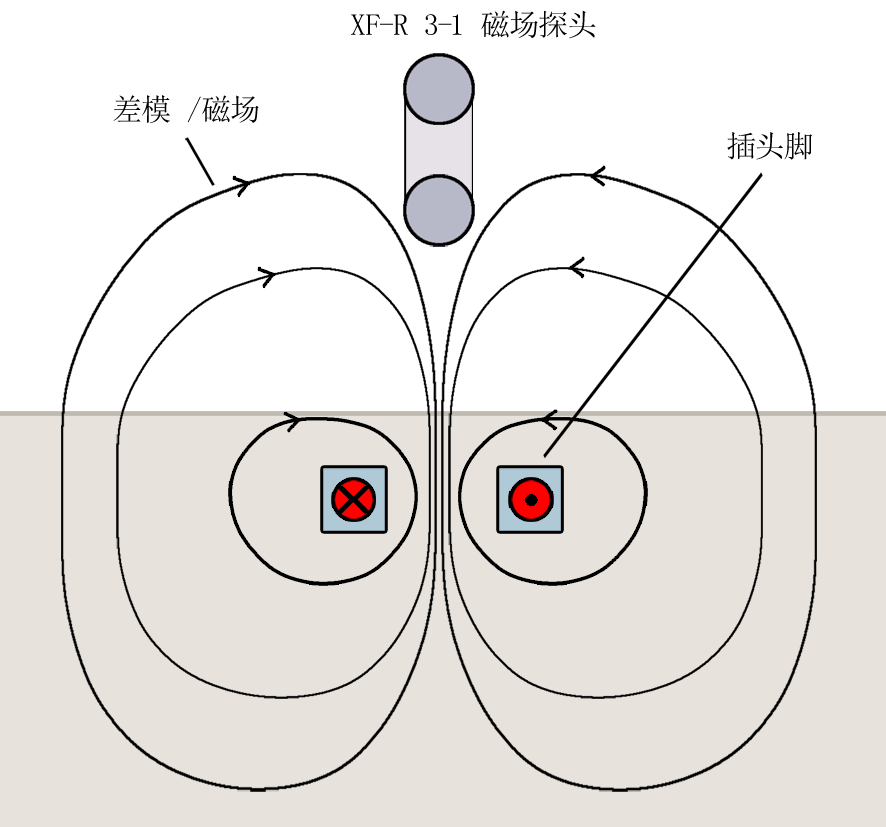

图2:使用近场探头XF-R 3-1测量LVDS线对的共模信号与差模信号

使用磁场探头XF-R3-1,能够测量接插连接器LVDS导线的共模和差模场。

图2示出了LVDS插头管脚和磁场探头XF-R 3-1的位置分布。通过测量磁场的方法测量共模电流,如图2a所示。测量时近场探头必须与LVDS线对垂直。如果它与LVDS线对平行,就无法借助磁场测量共模电流,如图2b所示。

与共模电流不同,测量差模电流时,近场探头必须保持与LVDS线对平行,如图2c所示。

如图所示,根据探头的不同位置,可以有选择地测量共模电流或者差模电流。图3示出了测量结果。

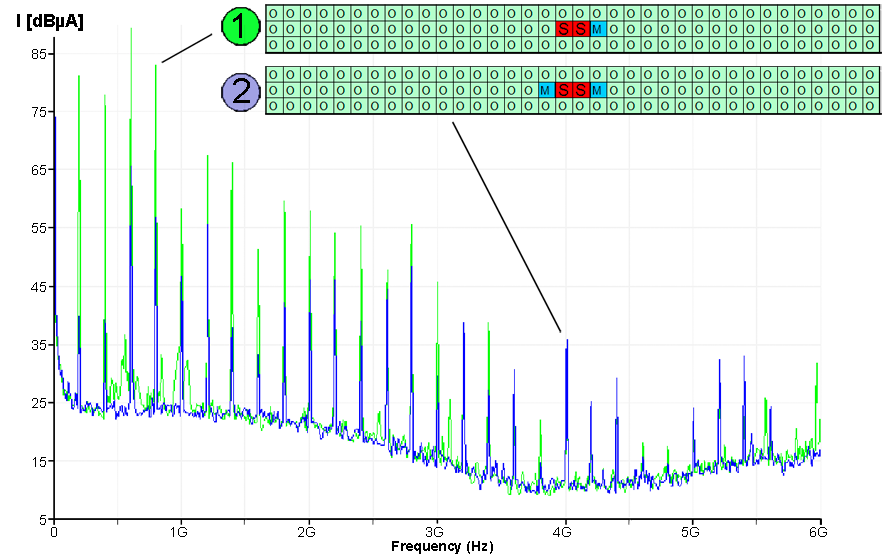

在2GHz以下的频率范围内,差模分量(绿色)占优势,而在2 - 4.4 GHz的频率范围内,共模分量(红色) 是主要的。通过电流校正因数,将磁场探头XF-R3-1的测定结果转换为电流值iErr。这一转换由测量软件ChipScan-ESA完成。

Gegentakt(gr) H-Korrektur_Chipscan-ESA_wPZ.png)

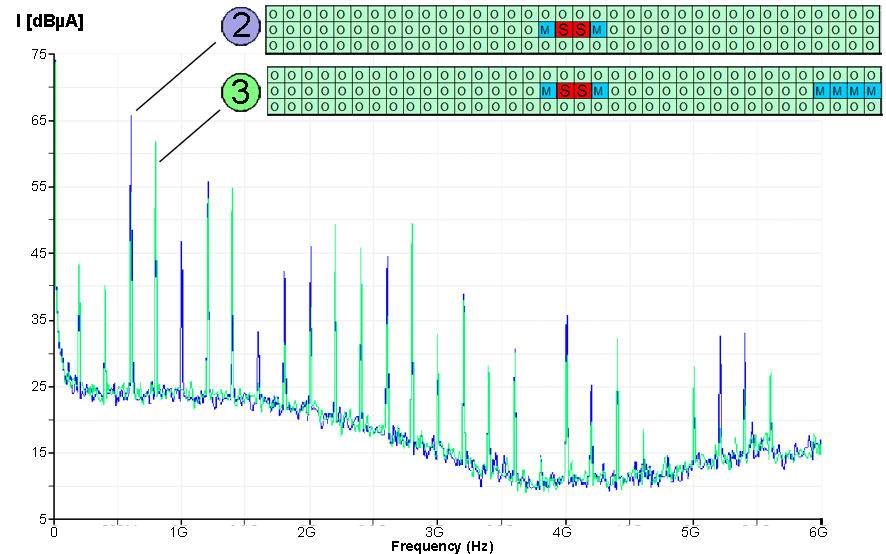

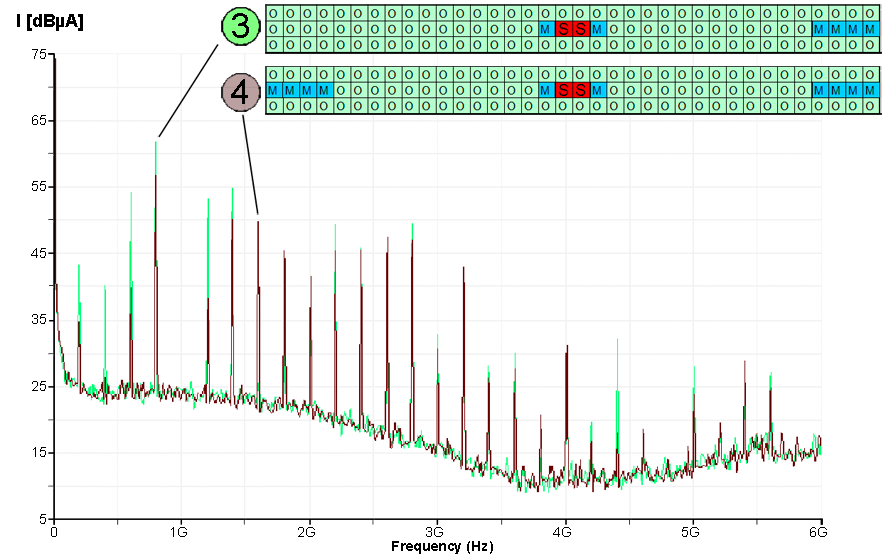

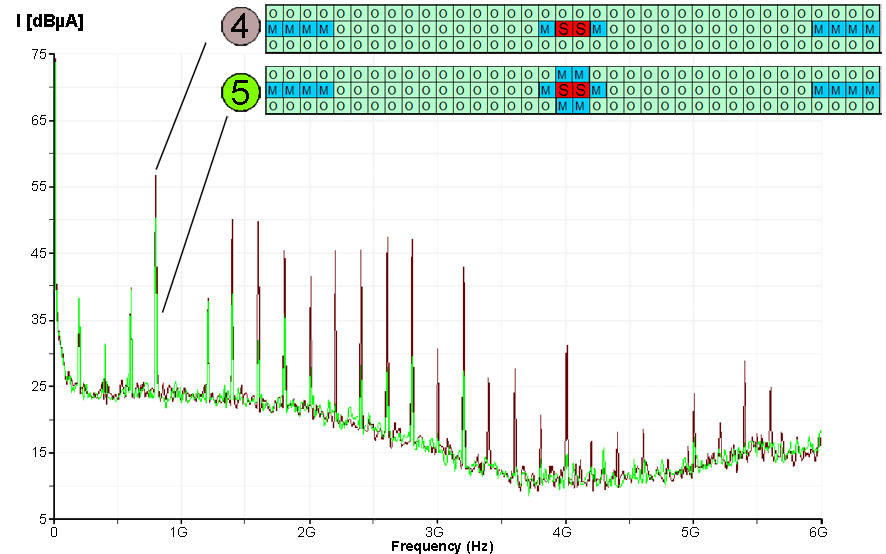

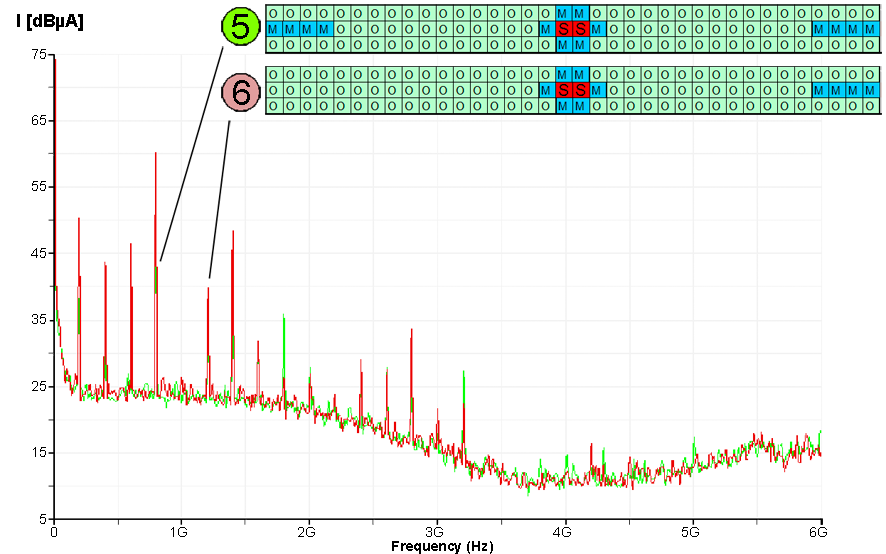

ChipScan-ESA芯片扫描系统特别适用于频谱分析仪测量曲线的比较分析。下列图中仅仅显示出该软件用户界面中的观察窗口部分。

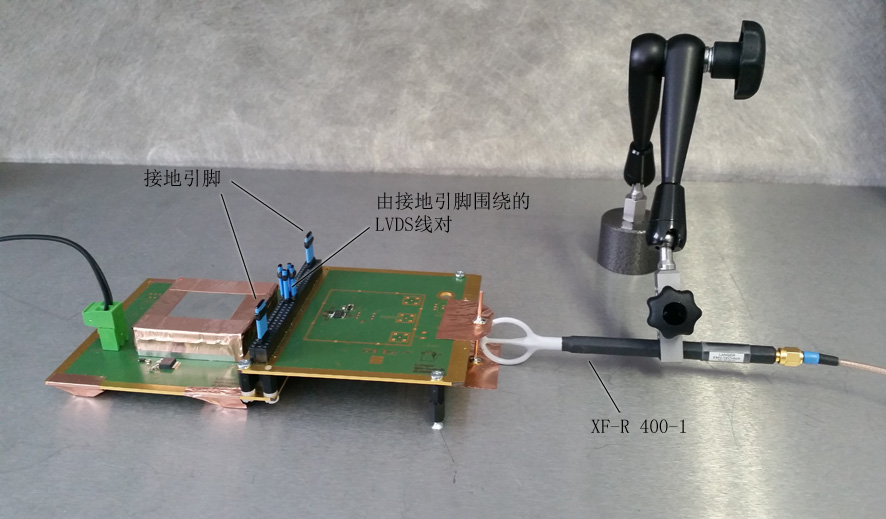

按照图1中的连接b,测量装置如图4所示。通过插拔式接地引脚(蓝色),可以改变接插连接器的接地分配。

LVDS线对位于接插连接器的中部,周围有接地引脚。使用的LVDS驱动器是IC LVDS100(2 Gbps)。

图5示意性地绘出了电流路径。

下面通过6个测量试验说明如何通过改变接插连接器的接地分配来减少干扰发射。

图6中显示了两种情况下测量的激励电流iErr:接地引脚非对称地分布在LVDS线对两边(例1) ;接地引脚对称地分布在LVDS线对两边(例2)。可以看出,在对称的情况下(例2),主要范围内(至2 GHz)的差模干扰减少(对照图3)。这意味着,对称布置LVDS线对周围的接地,对减少干扰发射至关重要,而仅仅保持驱动电流对称是不够的。这个例子表明,LVDS线对的周围电路也应该对称。

将例2的对称接地分布通过4个接地引脚转换成图7所示的非对称布置(,例3),测量结果显示激励电流iErr 没有明显地减少。干扰发射在整个范围内随机地增加和减少,最大幅度达10分贝。对于例3这种接地分布情况,两种分量的叠加效应导致差模耦合增加(变差)和共模耦合减少(改善)。两个分量能够相加或者相减,从而产生积极和消极的效果。

将例3非对称接地的情况转换成图8所示的对称接地分布(,例4)。在这种布置情况下,频率范围至1.5GHz的差模分量减少了。这意味着在接插连接器上,远离LVDS线对的接地也应该是对称的。

进一步改善LVDS线对周围的接地而形成(,例5)的布置,如图9所示,其共模耦合减少。但是由于对称性没有进一步提高,例5这种接地分布对差模耦合没有影响。

减少共模耦合的效果主要体现在中频和高频范围内。

通过拔掉4个接地引脚,接地分布不再对称而形成状态(例6),如图10所示。由于失去了对称性,在至1.5GHz的频率范围内,输出耦合会增加最多15分贝。

结论:

对干扰发射的抑制,不仅取决于LVDS线对附近接地屏蔽的对称性(例2),离LVDS线对较远的接地屏蔽的对称性也同样至关重要 (例5,效果改善高达15分贝)。